૧. EMC ના કારણો અને રક્ષણાત્મક પગલાં

હાઇ-સ્પીડ બ્રશલેસ મોટર્સમાં, EMC સમસ્યાઓ ઘણીવાર સમગ્ર પ્રોજેક્ટનું કેન્દ્ર અને મુશ્કેલી હોય છે, અને સમગ્ર EMC ની ઑપ્ટિમાઇઝેશન પ્રક્રિયામાં ઘણો સમય લાગે છે. તેથી, આપણે પહેલા EMC પ્રમાણભૂત અને અનુરૂપ ઑપ્ટિમાઇઝેશન પદ્ધતિઓ કરતાં વધુ હોવાના કારણોને યોગ્ય રીતે ઓળખવાની જરૂર છે.

EMC ઑપ્ટિમાઇઝેશન મુખ્યત્વે ત્રણ દિશાઓથી શરૂ થાય છે:

- દખલગીરીના સ્ત્રોતને સુધારો

હાઇ-સ્પીડ બ્રશલેસ મોટર્સના નિયંત્રણમાં, દખલગીરીનો સૌથી મહત્વપૂર્ણ સ્ત્રોત એ MOS અને IGBT જેવા સ્વિચિંગ ઉપકરણોથી બનેલો ડ્રાઇવ સર્કિટ છે. હાઇ-સ્પીડ મોટરના પ્રદર્શનને અસર કર્યા વિના, MCU કેરિયર ફ્રીક્વન્સી ઘટાડવાથી, સ્વિચિંગ ટ્યુબની સ્વિચિંગ સ્પીડ ઘટાડવાથી અને યોગ્ય પરિમાણો સાથે સ્વિચિંગ ટ્યુબ પસંદ કરવાથી EMC હસ્તક્ષેપ અસરકારક રીતે ઘટાડી શકાય છે.

- હસ્તક્ષેપ સ્ત્રોતના જોડાણ માર્ગને ઘટાડવો

PCBA રૂટીંગ અને લેઆઉટને ઑપ્ટિમાઇઝ કરવાથી EMC અસરકારક રીતે સુધારી શકાય છે, અને એકબીજા સાથે રેખાઓનું જોડાણ વધુ દખલગીરીનું કારણ બનશે. ખાસ કરીને ઉચ્ચ-આવર્તન સિગ્નલ લાઇનો માટે, લૂપ્સ બનાવતા ટ્રેસ અને એન્ટેના બનાવતા ટ્રેસ ટાળવાનો પ્રયાસ કરો. જો જરૂરી હોય તો કપ્લિંગ ઘટાડવા માટે શિલ્ડિંગ લેયર વધારી શકાય છે.

- દખલગીરી અટકાવવાના માધ્યમો

EMC સુધારણામાં સૌથી વધુ ઉપયોગમાં લેવાતા વિવિધ પ્રકારના ઇન્ડક્ટન્સ અને કેપેસિટર્સ છે, અને વિવિધ ઇન્ટરફરેન્સ માટે યોગ્ય પરિમાણો પસંદ કરવામાં આવે છે. Y કેપેસિટર અને કોમન મોડ ઇન્ડક્ટન્સ કોમન મોડ ઇન્ટરફરેન્સ માટે છે, અને X કેપેસિટર ડિફરન્શિયલ મોડ ઇન્ટરફરેન્સ માટે છે. ઇન્ડક્ટન્સ મેગ્નેટિક રિંગને હાઇ ફ્રીક્વન્સી મેગ્નેટિક રિંગ અને લો ફ્રીક્વન્સી મેગ્નેટિક રિંગમાં પણ વિભાજિત કરવામાં આવે છે, અને જ્યારે જરૂર પડે ત્યારે એક જ સમયે બે પ્રકારના ઇન્ડક્ટન્સ ઉમેરવાની જરૂર છે.

2. EMC ઑપ્ટિમાઇઝેશન કેસ

અમારી કંપનીની 100,000-rpm બ્રશલેસ મોટરના EMC ઑપ્ટિમાઇઝેશનમાં, અહીં કેટલાક મુખ્ય મુદ્દાઓ છે જે મને આશા છે કે દરેકને મદદરૂપ થશે.

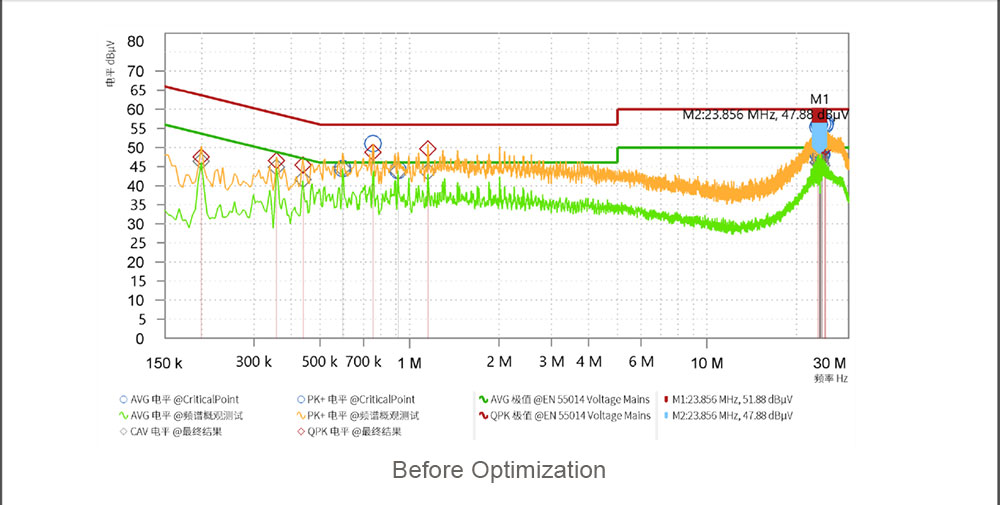

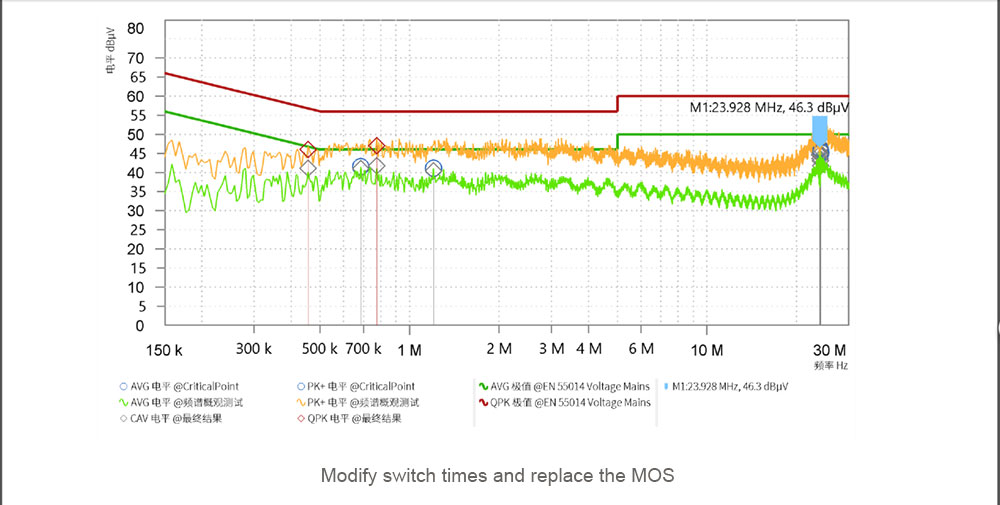

મોટરને એક લાખ રિવોલ્યુશનની ઊંચી ગતિ સુધી પહોંચાડવા માટે, પ્રારંભિક વાહક આવર્તન 40KHZ પર સેટ કરવામાં આવ્યું છે, જે અન્ય મોટરો કરતા બમણું વધારે છે. આ કિસ્સામાં, અન્ય ઑપ્ટિમાઇઝેશન પદ્ધતિઓ EMC ને અસરકારક રીતે સુધારવામાં સક્ષમ નથી. નોંધપાત્ર સુધારો થાય તે પહેલાં આવર્તન 30KHZ સુધી ઘટાડવામાં આવે છે અને MOS સ્વિચિંગ સમયની સંખ્યા 1/3 દ્વારા ઘટાડવામાં આવે છે. તે જ સમયે, એવું જાણવા મળ્યું કે MOS ના રિવર્સ ડાયોડનો Trrr (રિવર્સ રિકવરી સમય) EMC પર અસર કરે છે, અને ઝડપી રિવર્સ રિકવરી સમય સાથે MOS પસંદ કરવામાં આવ્યો હતો. પરીક્ષણ ડેટા નીચેની આકૃતિમાં બતાવ્યા પ્રમાણે છે. 500KHZ~1MHZ નું માર્જિન લગભગ 3dB વધ્યું છે અને સ્પાઇક વેવફોર્મ ફ્લેટ કરવામાં આવ્યું છે:

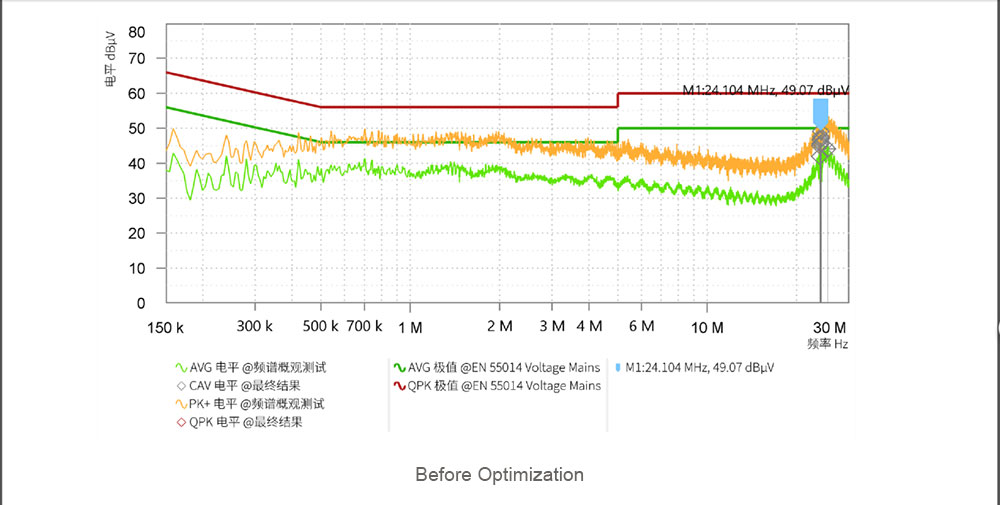

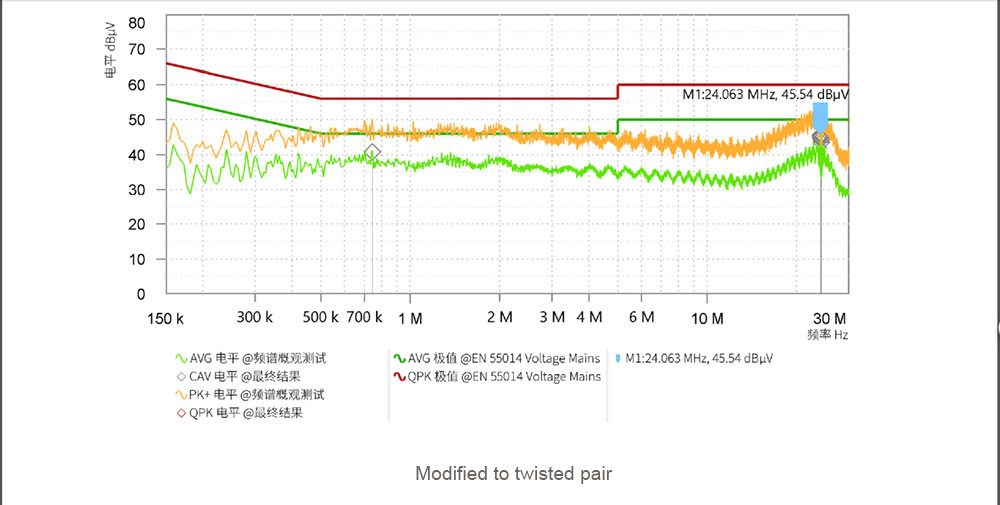

PCBA ના ખાસ લેઆઉટને કારણે, બે હાઇ-વોલ્ટેજ પાવર લાઇન છે જેને અન્ય સિગ્નલ લાઇન સાથે જોડવાની જરૂર છે. હાઇ-વોલ્ટેજ લાઇનને ટ્વિસ્ટેડ જોડીમાં બદલ્યા પછી, લીડ્સ વચ્ચેનો પરસ્પર દખલ ઘણો ઓછો થાય છે. પરીક્ષણ ડેટા નીચેની આકૃતિમાં બતાવ્યા પ્રમાણે છે, અને 24MHZ માર્જિન લગભગ 3dB વધ્યું છે:

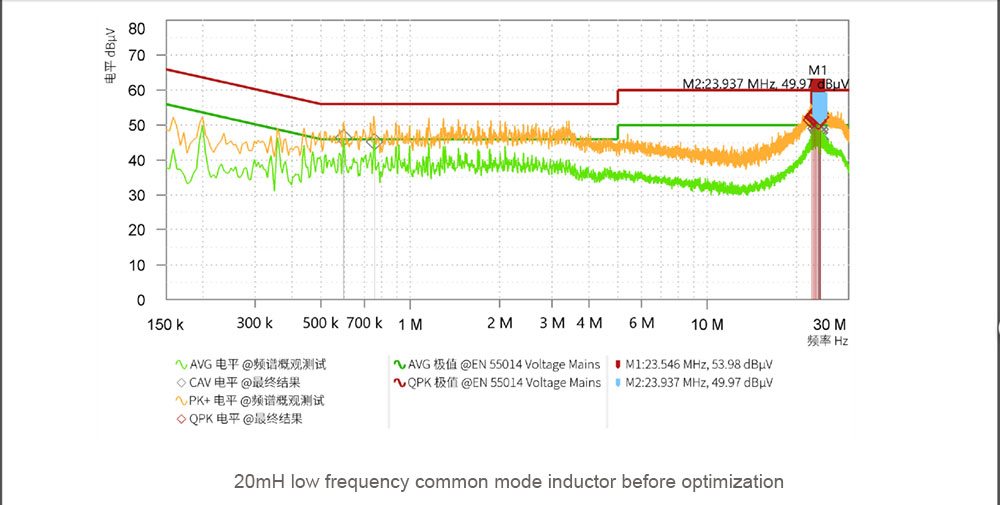

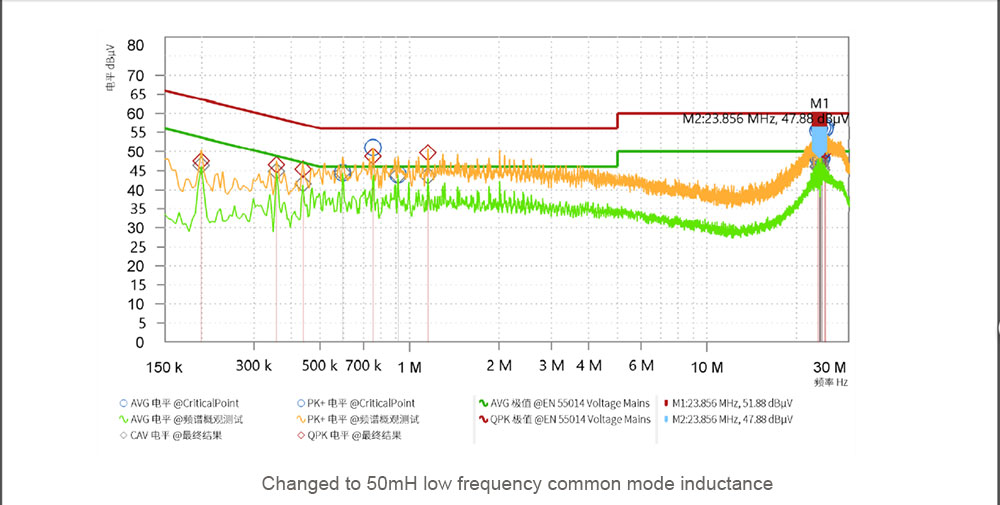

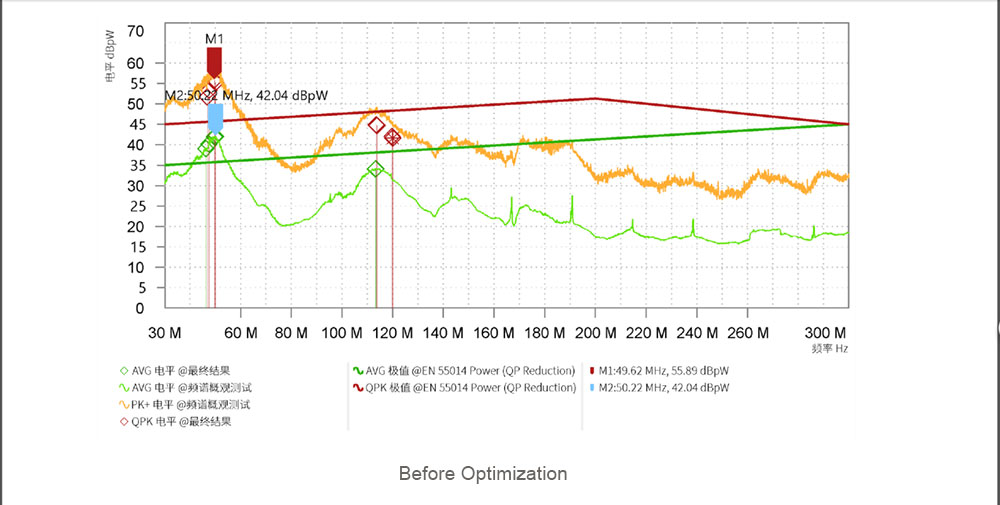

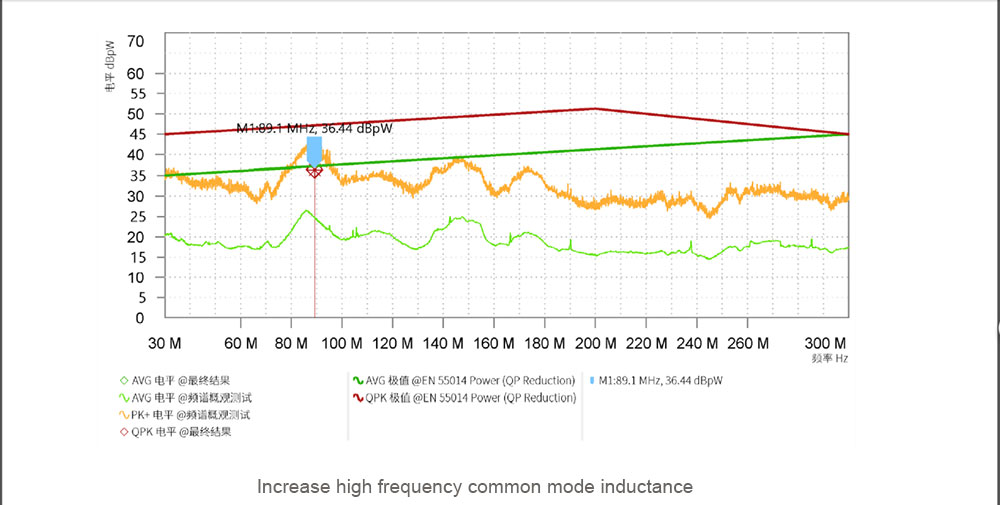

આ કિસ્સામાં, બે કોમન-મોડ ઇન્ડક્ટરનો ઉપયોગ કરવામાં આવે છે, જેમાંથી એક ઓછી-આવર્તન ચુંબકીય રિંગ છે, જે લગભગ 50mH ની ઇન્ડક્ટન્સ સાથે છે, જે 500KHZ ~ 2MHZ ની રેન્જમાં EMC ને નોંધપાત્ર રીતે સુધારે છે. બીજું ઉચ્ચ-આવર્તન ચુંબકીય રિંગ છે, જે લગભગ 60uH ની ઇન્ડક્ટન્સ સાથે છે, જે 30MHZ ~ 50MHZ ની રેન્જમાં EMC ને નોંધપાત્ર રીતે સુધારે છે.

ઓછી-આવર્તન ચુંબકીય રિંગનો પરીક્ષણ ડેટા નીચેની આકૃતિમાં બતાવવામાં આવ્યો છે, અને એકંદર માર્જિન 300KHZ~30MHZ ની રેન્જમાં 2dB દ્વારા વધારવામાં આવ્યો છે:

ઉચ્ચ-આવર્તન ચુંબકીય રિંગનો પરીક્ષણ ડેટા નીચેની આકૃતિમાં બતાવવામાં આવ્યો છે, અને માર્જિન 10dB કરતા વધુ વધ્યો છે:

મને આશા છે કે દરેક વ્યક્તિ EMC ઑપ્ટિમાઇઝેશન પર મંતવ્યો અને વિચાર-વિમર્શ કરી શકશે, અને સતત પરીક્ષણમાં શ્રેષ્ઠ ઉકેલ શોધી શકશે.

પોસ્ટ સમય: જૂન-૦૭-૨૦૨૩